1. Achosion EMC a mesurau amddiffynnol

Mewn moduron di-frwsh cyflym, problemau EMC yn aml yw ffocws ac anhawster y prosiect cyfan, ac mae'r broses optimeiddio ar gyfer yr EMC cyfan yn cymryd llawer o amser. Felly, mae angen inni gydnabod yn gywir yr achosion pam mae EMC yn rhagori ar y safon a'r dulliau optimeiddio cyfatebol yn gyntaf.

Mae optimeiddio EMC yn dechrau o dair cyfeiriad yn bennaf:

- Gwella ffynhonnell yr ymyrraeth

Wrth reoli moduron di-frwsh cyflymder uchel, y ffynhonnell ymyrraeth bwysicaf yw'r gylched yrru sy'n cynnwys dyfeisiau newid fel MOS ac IGBT. Heb effeithio ar berfformiad y modur cyflymder uchel, gall lleihau amledd cludwr yr MCU, lleihau cyflymder newid y tiwb newid, a dewis y tiwb newid gyda pharamedrau priodol leihau ymyrraeth EMC yn effeithiol.

- Lleihau llwybr cyplu'r ffynhonnell ymyrraeth

Gall optimeiddio llwybro a chynllun PCBA wella EMC yn effeithiol, a bydd cyplu llinellau i'w gilydd yn achosi mwy o ymyrraeth. Yn enwedig ar gyfer llinellau signal amledd uchel, ceisiwch osgoi'r olion sy'n ffurfio dolenni a'r olion sy'n ffurfio antenâu. Os oes angen, gellir cynyddu'r haen amddiffyn i leihau'r cyplu.

- Dulliau o rwystro ymyrraeth

Y mathau mwyaf cyffredin o anwythiadau a chynwysyddion a ddefnyddir mewn gwelliant EMC, a dewisir paramedrau addas ar gyfer gwahanol ymyriadau. Mae cynhwysydd Y ac anwythiad modd cyffredin ar gyfer ymyrraeth modd cyffredin, ac mae cynhwysydd X ar gyfer ymyrraeth modd gwahaniaethol. Mae'r cylch magnetig anwythiad hefyd wedi'i rannu'n gylch magnetig amledd uchel a chylch magnetig amledd isel, ac mae angen ychwanegu dau fath o anwythiadau ar yr un pryd pan fo angen.

2. Achos optimeiddio EMC

Wrth optimeiddio EMC modur di-frwsh 100,000-rpm ein cwmni, dyma rai pwyntiau allweddol yr wyf yn gobeithio y byddant o gymorth i bawb.

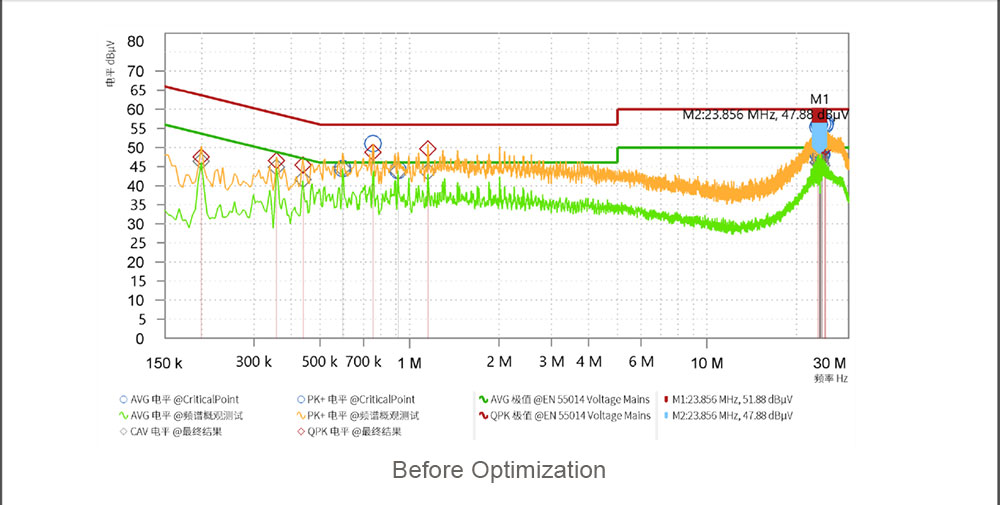

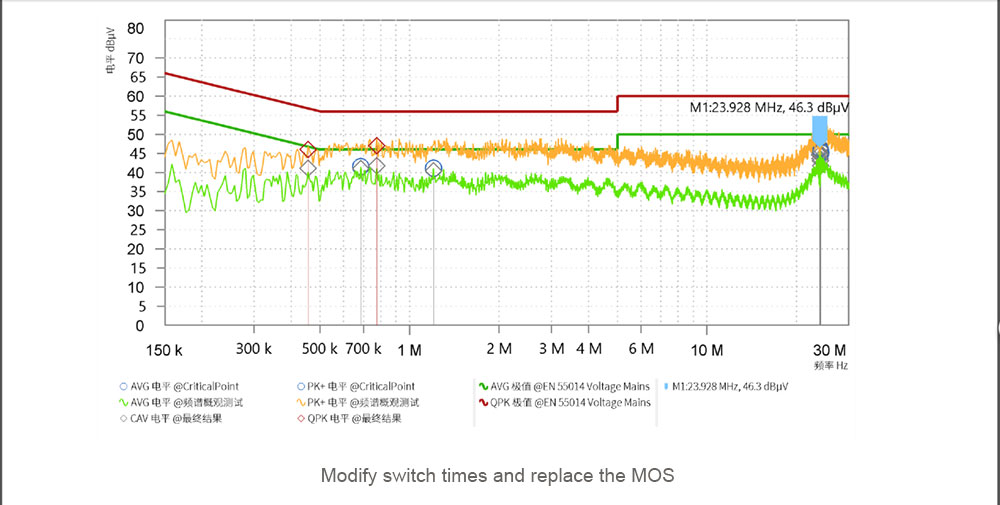

Er mwyn i'r modur gyrraedd cyflymder uchel o gant mil o chwyldroadau, mae amledd y cludwr cychwynnol wedi'i osod i 40KHZ, sydd ddwywaith yn uwch na moduron eraill. Yn yr achos hwn, nid yw dulliau optimeiddio eraill wedi gallu gwella EMC yn effeithiol. Mae'r amledd wedi'i leihau i 30KHZ a chaiff nifer yr amseroedd newid MOS ei leihau 1/3 cyn bod gwelliant sylweddol. Ar yr un pryd, canfuwyd bod Trr (amser adfer gwrthdro) deuod gwrthdro'r MOS yn cael effaith ar EMC, a dewiswyd MOS gydag amser adfer gwrthdro cyflymach. Mae'r data prawf fel y dangosir yn y ffigur isod. Mae'r ymyl o 500KHZ ~ 1MHZ wedi cynyddu tua 3dB ac mae'r donffurf pigyn wedi'i fflatio:

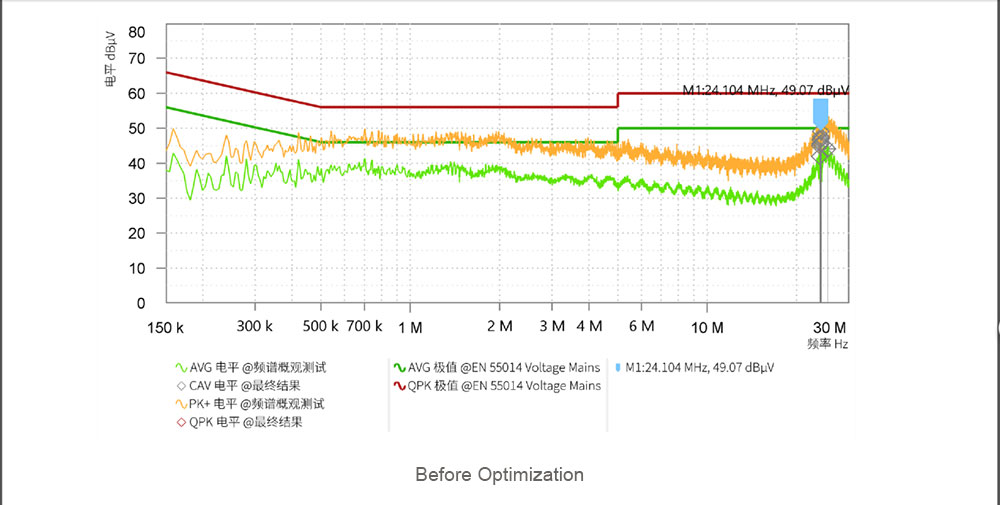

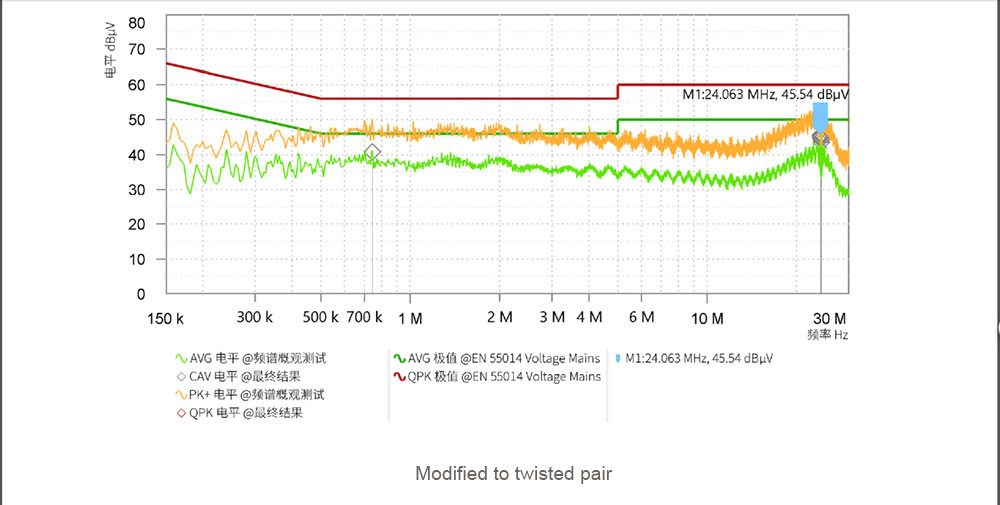

Oherwydd cynllun arbennig y PCBA, mae dau linell bŵer foltedd uchel y mae angen eu bwndelu â llinellau signal eraill. Ar ôl i'r llinell foltedd uchel gael ei newid i bâr dirdro, mae'r ymyrraeth gydfuddiannol rhwng y gwifrau yn llawer llai. Mae data'r prawf fel y dangosir yn y ffigur isod, ac mae'r ymyl 24MHZ wedi cynyddu tua 3dB:

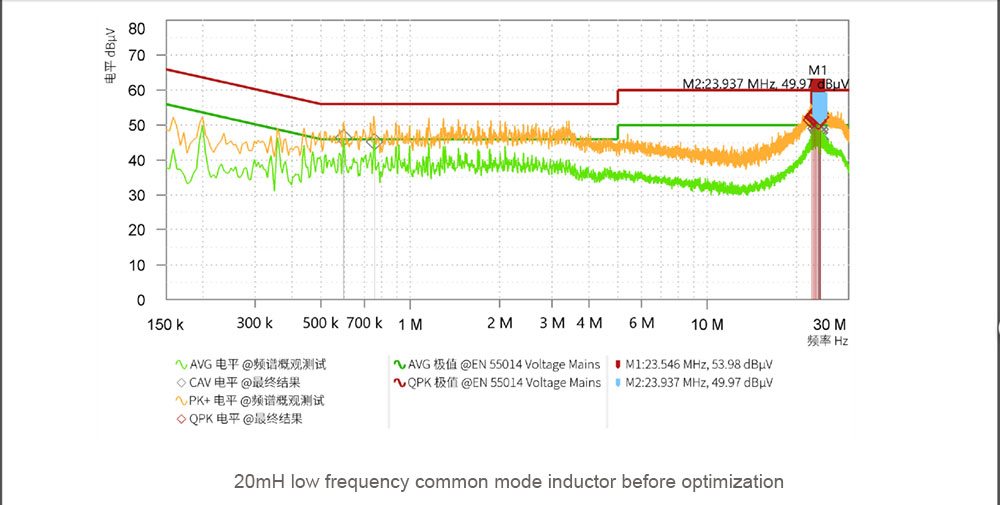

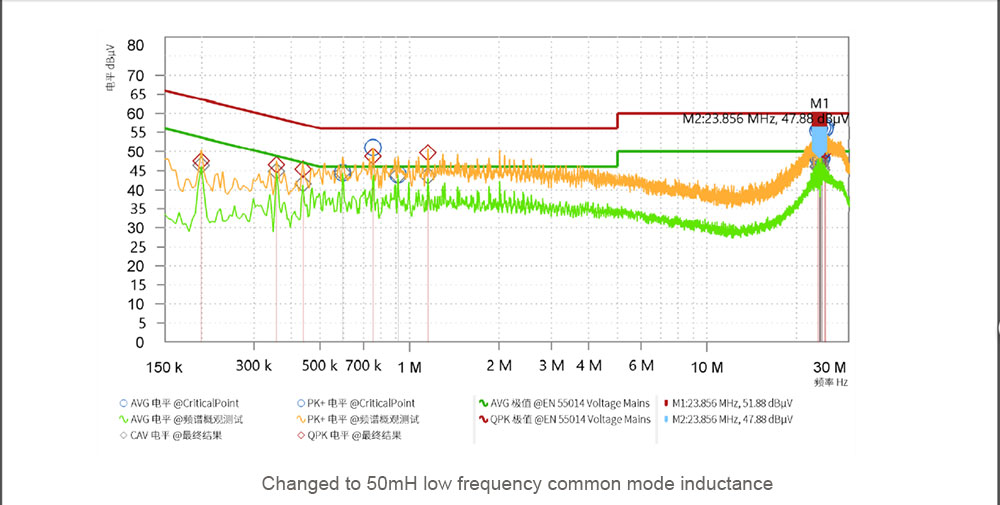

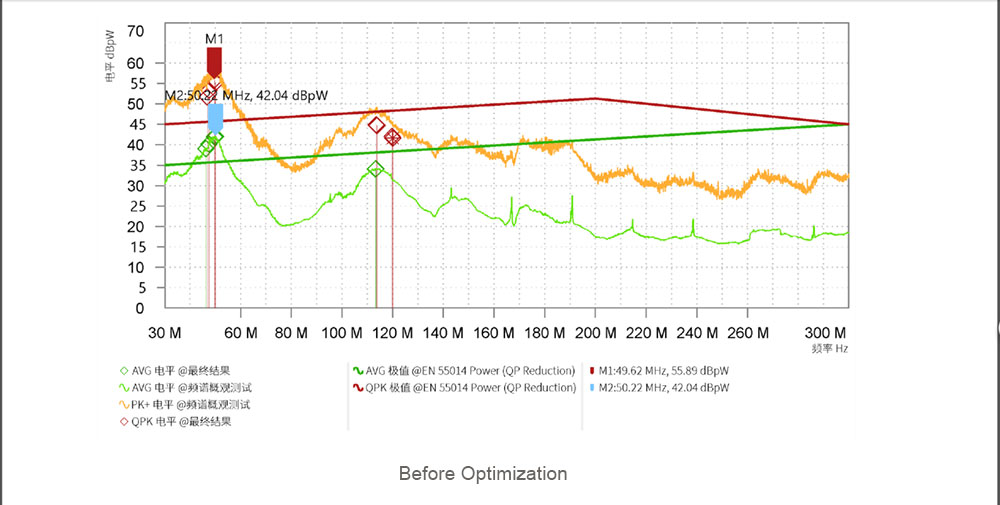

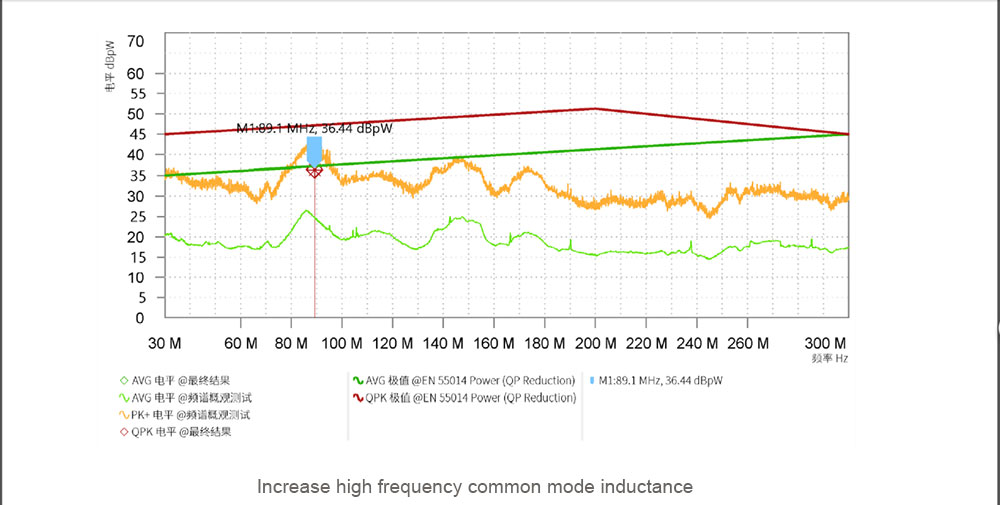

Yn yr achos hwn, defnyddir dau anwythydd modd cyffredin, ac mae un ohonynt yn gylch magnetig amledd isel, gydag anwythiad o tua 50mH, sy'n gwella EMC yn sylweddol yn yr ystod o 500KHZ ~ 2MHZ. Y llall yw cylch magnetig amledd uchel, gydag anwythiad o tua 60uH, sy'n gwella EMC yn sylweddol yn yr ystod o 30MHZ ~ 50MHZ.

Dangosir data prawf y cylch magnetig amledd isel yn y ffigur isod, ac mae'r ymyl cyffredinol yn cynyddu 2dB yn yr ystod o 300KHZ ~ 30MHZ:

Dangosir data prawf y cylch magnetig amledd uchel yn y ffigur isod, ac mae'r ymyl wedi cynyddu mwy na 10dB:

Gobeithio y gall pawb gyfnewid barn a meddwl am optimeiddio EMC, a dod o hyd i'r ateb gorau mewn profion parhaus.

Amser postio: Mehefin-07-2023